|

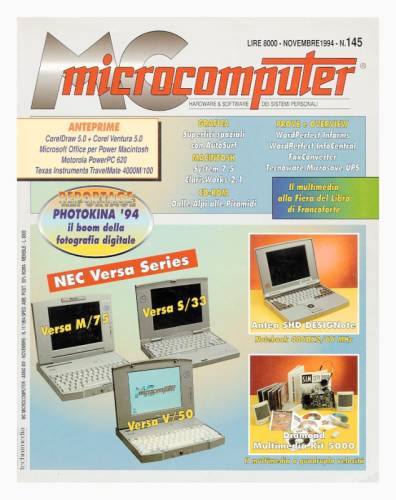

Articolo pubblicato sul n. 145 di MCmicrocomputer (Edizioni Technimedia Srl - Roma) nel novembre 1994

Anteprima:

Sin

dalla presentazione del primo PowerPC, l'ormai noto 601 gia'

installato in tutti i Power Macintosh, vennero indicati

anche i suoi successori: il 603, il 604 e il 620. I primi

due, 603 e 604, hanno gia' visto la luce rispettivamente

alla fine dell'anno scorso e nella primavera di quest'anno.

Mancava all'appello (ma non si e' fatto certo aspettare) la

vera e propria bomba: il 620, la massima espressione

dell'eccezionale potenza elaborativa dell'architettura

PowerPC. L'annuncio e' stato dato, congiuntamente da IBM e

Motorola, il 17 ottobre scorso in contemporanea allo SMAU.

Architettura a 64 bit

Il microprocessore 620 rappresenta la prima realizzazione a 64 bit dell'architettura PowerPC pur mantenendo la piena compatibilita' software con tutte le esistenti applicazioni a 32 bit. Grazie alle sue capacita' di multielaborazione, di calcolo numerico intensivo e di calcolo in virgola mobile, il PowerPC 620 rappresenta il microprocessore ideale per le esigenze dei server e delle workstation piu' potenti. Dai test effettuati, il PowerPC 620 a 133 MHz (ma presto arrivera' anche la versione a 150 MHz) ha raggiunto lo strabiliante risultato di 225 SPECin92 e 300 SPECfp92. Per fare un paragone, la versione a 100 megahertz del 601 fornisce i valori, rispettivamente, di 105 e 125, il 604 arriva a 160 e 165. Il primo in aritmetica intera, il secondo in virgola mobile, SPECin92 e SPECfp92 come noto sono test di velocita' basati su prove standard e orientate alle applicazioni. Sono stati messi a punto dall'organizzazione senza scopi di lucro Standard Performance Evaluation Council (SPEC). Tornando al PowerPC 620, e' da segnalare che il rapporto tra la velocita' di clock interna e quella del bus di sistema puo' essere 2:1, 3:1 o 4:1. Potranno esistere, dunque, sia macchine con il bus a 33 MHz e velocita' del processore di 133 MHz che macchine utilizzanti il medesimo microprocessore ma con un bus di sistema a 66 MHz. Come per il 604, anche il 620 e' realizzato in tecnologia CMOS da 0.5 micron, funziona a 3.3 volt, ma incorpora ben sette milioni di transistor. Al suo interno sono presenti due cache per dati e istruzioni da 32 kbyte l'una dotate di altri 4 kbyte di bit di parita' per l'integrita' dei dati e delle istruzioni mantenute all'interno del chip.

Interfacciamento processore memoria

Dotato di un'interfaccia ad alta velocita' con la memoria, il PowerPC 620 integra al suo interno anche il controller della cache di secondo livello (esterna al processore), un bus a 128 bit ed ampie capacita' di multielaborazione. Grazie alla sua architettura superscalare (durata media delle istruzioni inferiore al singolo ciclo di clock) puo' inviare contemporaneamente fino a quattro istruzioni in parallelo a sei unita' di esecuzione indipendenti. Queste sono l'unita' in virgola mobile (FPU), l'unita' di processo per i salti (BPU), l'unita' load/store piu' tre unita' intere, due a ciclo singolo e una a ciclo multiplo. Le sei unita', in quanto indipendenti, operano assolutamente in parallelo e possono quindi completare l'esecuzione di ben sei istruzioni contemporaneamente. L'interfacciamento esterno di avvale di un bus di indirizzamento a 40 bit e puo' essere configurato per utilizzare un bus dati da 64 o 128 bit. Per entrambi i bus sono previsti rispettivamente 3 e 16 bit di parita' oltre naturalmente ad una serie di segnali di controllo per l'ottimizzazione a vari livelli di sistema. Il protocollo di interfaccia consente a piu' microprocessori di concorrere per le risorse di sistema attraverso l'utilizzo di un meccanismo di arbitraggio esterno centralizzato. La logica incorporata nel chip mantiene la coerenza tra le cache nell'utilizzo in sistemi multiprocessor. Gli accessi in memoria da parte del PowerPC 620 non avvengono secondo un ordine rigido. Sequenze di operazioni, incluso la lettura/scrittura multipla di stringhe, non necessariamente viene completata nello stesso ordine in cui sono iniziate, massimizzando l'efficienza del bus senza sacrificare la coerenza dei dati. E' anche possibile, se non sussistono problemi di dipendenza, che le operazioni di lettura precedano quelle di scrittura quando questo provochi un aumento delle prestazioni generali.

Da Power a PowerPC

Power sta per Performance Optimized With Enhanced RISC ed e' l'architettura sviluppata da IBM, ormai alcuni anni or sono, per le sue macchine RS/6000. PowerPC e' un'implementazione single chip a basso costo dell'architettura Power (con la quale non va confusa). Quest'ultima dispone di tre unita' esecutive indipendenti (una branch unit, una integer unit e una floating-point unit) grazie alle quali istruzioni differenti possono essere eseguite parallelamente e nel medesimo ciclo di clock. Diversamente dalle comuni architetture RISC, nei processori Power delle macchine RS/6000, il formato floating point e' compreso tra i tipi di dato di prima classe: non viene considerato come una caratteristica opzionale e trattato da un coprocessore, ma e' direttamente implementato nel set istruzioni del processore stesso esattamente come i tipi di dato standard, interi e logici. Il set di istruzioni floating point comprende una serie di istruzioni "moltiplica-e-somma" che consentono di migliorare drasticamente le prestazioni di molti algoritmi. Nell'implementazione di PowerPC, il set di istruzioni di Power e' stato ridimensionato per facilitare la realizzazione di versioni single chip a basso costo. Contemporaneamente alcune funzioni sono state eliminate per semplificare la realizzazione di versioni superscalari molto aggressive. Inoltre, l'architettura e' stata estesa integralmente a 64 bit, per prolungare il ciclo di vita di PowerPC, partendo da una piattaforma sufficiente a coprire tutte le esigenze di calcolo dei prossimi dieci anni. Per garantire comunque la totale compatibilita' con le applicazioni Power, tutte le funzioni non piu' residenti possono essere implementate attraverso meccanismi di "trap & emulate". A fronte delle relative esemplificazioni, troviamo d'altro canto un potenziamento del set di istruzioni per schedulare esplicitamente i dati da introdurre ed estrarre sotto il controllo dell'utente, nonche' l'aggiunta di istruzioni floating point in singola precisione (Power supporta solo la doppia precisione). Ma il cambiamento piu' significativo da Power a PowerPC riguarda, come detto, l'estensione dell'architettura da 32 a 64 bit: con l'annuncio del dispositivo 620 la famiglia comprende sia PowerPC a 32 che a 64 bit, ma tutti i processori sono in grado di lavorare a 32 bit. Cio' consente alle applicazioni a 32 bit di girare anche sui dispositivi a 64 bit con un kernel di sistema operativo a in quest'ultimo formato, permettendo allo stesso tempo alle nuove applicazioni a 64 bit di utilizzare le esistenti librerie a 32.

Dicono di PowerPC 620 (fonte IBM e Motorola)

"L'alleanza (IBM-Motorola-Apple, ndr) ha sviluppato un microprocessore dalle prestazioni superiori. Come e' gia' avvenuto per gli altri modelli della famiglia PowerPC, siamo convinti che il microprocessore 620 superera' le prestazioni di analoghi dispositivi della concorrenza acquisendo la leadership per quanto riguarda il rapporto prestazioni/prezzo anche nel nuovo segmento di mercato"

Les Crudele Vice Presidente e Direttore Generale Divisione Microprocessori RISC di Motorola

"I clienti sanno che questa alleanza intende guidare la fase di mutamento che sta attraversando tutta l'industria dei microprocessori e che noi continueremo a fornire loro prodotti all'avanguardia sul mercato. Recenti avvenimenti nell'industria hanno dimostrato che i nostri concorrenti si sono finalmente resi conto di cio' che i nostri clienti sapevano da un pezzo e cioe' che la tecnologia RISC e' grandemente vantaggiosa. Nessun altro microprocessore rappresenta una realizzazione RISC migliore del PowerPC"

Phil Hester General Manager System Technology and Architecture Division di IBM

"L'odierno annuncio conferma l'impegno assunto da Apple-IBM-Motorola nello sviluppare e produrre la famiglia piu' completa e potente di microprocessori RISC oggi sul mercato. Siamo molto soddisfatti della puntualita' che caratterizza il cammino della famiglia e siamo determinati a continuare la collaborazione con IBM e Motorola per migliorare i microprocessori PowerPC esistenti e sviluppare nuovi prodotti basati su questa architettura"

Howard Lee Senior Vice President Divisione Personal Computer di Apple

Articolo pubblicato su www.digiTANTO.it - per ulteriori informazioni clicca qui |