|

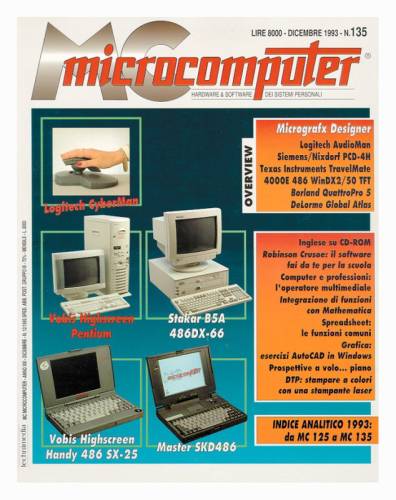

Articolo pubblicato sul n. 135 di MCmicrocomputer (Edizioni Technimedia Srl - Roma) nel dicembre 1993

Anteprima:

Se da

una parte siamo in molti a credere in un futuro RISC

dell'informatica personale e non, in Motorola non vi e'

naturalmente nessuna intenzione di abbandonare le macchine

CISC, quantomeno per quel che riguarda l'evoluzione di

famiglie preesistenti. Quella del 68000, ad esempio, era

ferma da circa tre anni al suo attuale modello di punta, il

68040, utilizzato ormai gia'

Descrizione

Il Motorola MC 68060 e' un processore a 32 bit ad alte prestazioni, superscalare, compatibile con tutta la famiglia 68000, e con possibilita' di operare a basso consumo. Al suo interno, gli oltre due milioni di transistor, integrati in tecnologia 0.5 micron triplo strato di metallizzazione funzionanti a 3.3 V, implementano una doppia cache interna, due indipendenti demand-page MMU sia per i dati che per le istruzioni, una doppia pipeline per le istruzioni intere, un'unita' floating point e una branch target cache. Un alto grado di parallelismo interno e' ottenuto attraverso l'utilizzo di architettura interna Harward, bus interni multipli, unita' di esecuzione indipendenti che permettono l'esecuzione parallela di due istruzioni. Una parte chiave del nuovo 68060 e' rappresentata dal cosiddetto "power management" che permette di traslare via software, attraverso l'istruzione LPSTOP, al modo di funzionamento a basso assorbimento. Oltre a questo, essendo realizzato in tecnologia "static", quando il chip non e' utilizzato, non assorbe corrente. Inoltre ogni unita' interna puo' essere singolarmente disabilitata per ricevere l'opportuna alimentazione solo durante il suo effettivo utilizzo.

Performance

Le simulazioni attualmente effettuate da Motorola indicano un incremento di circa il 50-70% dovuto alla nuova architettura e del 100% grazie al clock raddoppiato. Rispetto quindi ad un 68040 a 25 MHz, il futuro 68060 a 50 MHz andra' piu' del triplo piu' veloce. Tutto cio' senza effettuare ricompilazione del codice: ottimizzando anche questo ci si aspetta di ottenere un ulteriore 15-25% in piu'. Il 68060 e' una macchina a parallelismo interno spinto contenente al suo interno una sezione instruction-fecth indipendente da una unita' di esecuzione superscalare. Un'apposita cache per i branch e' utilizzata per ridurre i tempi di ritardo dovuti ai salti effettuati in una architettura pipeline come quella del 68060: basandosi sulla "storia" precedente del codice in esecuzione e' in grado di predire (statisticamente parlando) il fecth del flusso di istruzioni. L'Instruction Fetch Pipeline provvede a fornire all'Operand Execution Pipeline un continuo flusso di istruzioni da eseguire. Questa contiene a sua volta due pipeline parallele che permettono di eseguire piu' di un'istruzione completa in ogni ciclo di clock (da qui il fatto di essere superscalare). L'architettura Harward del 68060 fa si' che siano possibili accessi simultanei tanto alla cache istruzioni che alla cache dati. Inoltre, per raggiungere performance superscalari, la cache dei dati e' a sua volta "multiported" per un accesso simultaneo da parte delle due pipeline parallele della Operand Execution Unit. Articolo pubblicato su www.digiTANTO.it - per ulteriori informazioni clicca qui |